# Automatic Parallelization and Scheduling of Programs on **Multiprocessors using CASCH**

Ishfaq Ahmad<sup>1</sup>, Yu-Kwong Kwok<sup>1</sup>, Min-You Wu<sup>2</sup> and Wei Shu<sup>2</sup>

<sup>1</sup>Department of Computer Science, The Hong Kong University of Science and Technology, Hong Kong <sup>2</sup>Department of Computer Science, State University of New York at Buffalo, New York Email: {iahmad, csricky}@cs.ust.hk, {wu, shu}@cs.buffalo.edu

## Abstract<sup>†</sup>

The lack of a versatile software tool for parallel program development has been one of the major obstacles for exploiting the potential of high-performance architectures. In this paper, we describe an experimental software tool called CASCH (Computer Aided SCHeduling) for parallelizing and scheduling applications to parallel processors. CASCH transforms a sequential program to a parallel program with automatic scheduling, mapping, communication, and synchronization. The major strength of CASCH is its extensive library of scheduling and mapping algorithms representing a broad range of state-of-the-art work reported in the recent literature. These algorithms are applied for allocating a parallelized program to the processors, and thus the algorithms can be interactively analyzed, tested and compared using real data on a common platform with various performance objectives. CASCH is useful for both novice and expert programmers of parallel machines, and can serve as a teaching and learning aid for understanding scheduling and mapping algorithms.

## 1 Introduction

Parallel machines provide tremendous potential for high performance but their programming can be a tedious task. The software development process for parallel processing includes designing a parallel algorithm, partitioning the data and control, communication, synchronization, scheduling, mapping, and identifying and interpreting various performance measures. While an efficient implementation of some of these tasks can only be done manually, a number of tedious chores, such as scheduling, mapping, and communication can be automated.

Several research efforts have demonstrated the usefulness of program development tools for parallel processing. Essentially, these tools can be classified into two types. The first type of tools are mostly commercial tools which provide software development and debugging environments [5], [6], [10]. Some of these tools also provide performance tuning and other program development facilities [3], [11], [19]. A major drawback of some of these tools is that they are essentially simulation environments. While they can help in understanding the operation and behavior of scheduling and mapping algorithms, they are inadequate for practical purposes. The second type of tools performs some program transformation through program restructuring [7], [9], [13], [17], [22], [23], [24]. However, these tools are usually not well integrated with sophisticated scheduling algorithms.

In this paper, we describe a software tool called CASCH

(Computer Aided SCHeduling) for parallel processing on distributed-memory multiprocessors. CASCH can be considered to be a super set of tools such as PAWS [19], Hypertool [23], PYRROS [24], and Parallax [17], since it includes the major functionalities of these tools at a more advanced and comprehensive level and also offers additional useful features. CASCH is aimed to be a complete parallel programming environment including parallelization. partitioning, scheduling, mapping, communication, synchronization, code generation, and performance evaluation. Parallelization is performed by a compiler that automatically converts sequential applications into parallel codes. The parallel code is optimized through proper scheduling and mapping, and is executed on a target machine. CASCH provides an extensive library of state-of-the-art scheduling algorithms from the recent literature. The library of scheduling algorithms is organized into different categories which are suitable for different architectural environments.

The scheduling and mapping algorithms are used for scheduling the task graph generated from the user program. The weights on the nodes and edges of the task graph are computed using a database that contains the timing of various computation, communication, and I/O operations for different machines. These timings are obtained through benchmarking. An attractive feature of CASCH is its easy-to-use GUI for analyzing various scheduling and mapping algorithms using task graphs generated randomly, interactively, or directly from real programs. The best schedule generated by an algorithm can be used by the code generator for generating a parallel program for a particular machine-the same process can be repeated for another machine.

The rest of this paper is organized as follows. Section 2 gives an overview of CASCH and describes it major functionalities. Section 3 includes the results of the experiments conducted on the Intel Paragon using CASCH. The last section includes a discussion of the future work and some concluding remarks.

# **2** Overview of CASCH

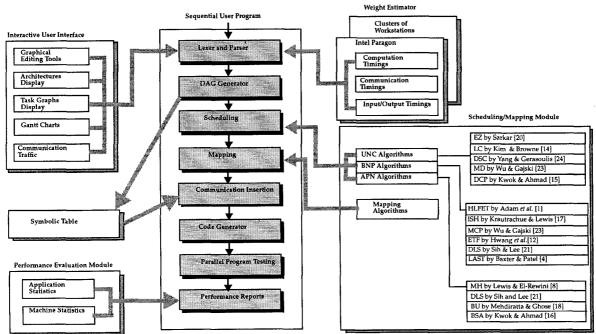

The overall organization of CASCH is shown in Figure 1. The main components of CASCH includes:

- A compiler which includes a lexer and a parser;

- A DAG (directed acyclic graph) generator;

- A weight estimator;

- A scheduling/mapping tool;

- A communication inserter;

- An interactive display unit;

- A code generator;

- A performance evaluation module.

These components are described below.

User Programs: Using the CASCH tool, the user first writes a sequential program from which a DAG is generated.

t. This research was partly supported by a grant from the Hong Kong Research Grants Council under contract number HKUST 734/96E and HKUST RI 93/94.EG06.

To facilitate the automation of program development, we use a programming style in which a program is composed of a set of procedures called from the main program. A procedure is an indivisible unit of computation to be scheduled on one processor. The grain sizes of procedures are determined by the programmer, and can be modified with CASCH.

The control dependencies can be ignored, so that a procedure call can be executed whenever all input data of the procedure are available. Data dependencies are defined by the single assignment of parameters in procedure calls. Communications are invoked only at the beginning and the end of procedures. In other words, a procedure receives messages before it begins execution, and it sends messages after it has finished the computation.

Lexer and Parser: The lexer and parser analyze the data dependencies and user defined partitions. For a static program, the number of procedures are known before program execution. Such a program can be executed sequentially or in parallel. It is system independent since communication primitives are not specified in the program. Data dependencies among the procedural parameters define a macro dataflow graph.

Weight Estimator: The weights on the nodes and edges of the DAG are inserted with the help of an estimator that provides timings of various instructions as well as the cost of communication on a given machine. The estimator uses actual timings of various computation, communication, and I/O operations on various machines. These timings are obtained through benchmarking using an approach similar to [19]. Communication estimation, which is obtained experimentally, is based on the cost for each communication primitive, such as *send*, *receive*, and *broadcast*.

**DAG Generation:** A macro dataflow graph, which is generated directly from the main program, is a directed graph with a start and an end point. Each node corresponds to a

procedure, and the node weight is represented by the procedure execution time. Each edge corresponds to a message transferred from one procedure to another procedure, and the weight of the edge is equal to the transmission time of the message. When two nodes are scheduled to a single processor, the weight of the edge connecting them becomes zero. The execution time of a node is obtained by using the estimator. The transmission time of a message is estimated by using the message start-up time, message length, and communication channel bandwidth.

Scheduling/Mapping Tool: A common approach to distributing workload to processors is to partition a problem into P tasks and perform a one-to-one mapping between the tasks and the processors. Partitioning can be done with the "block", "cyclic", or "block-cyclic" pattern [10]. Such partitioning schemes are suitable for problems with regular structures. Simple scheduling heuristics such as the "owner compute" rule work for certain problems but could fail for many others, especially for irregular problems, as it is difficult to balance load and minimize dependencies simultaneously. The way to solve irregular problems is to partition the problem into many tasks which are scheduled for a balanced load and minimized communication. In CASCH, a DAG generated based on this partitioning is scheduled using a scheduling algorithm. However, one scheduling algorithm may not be suitable for a certain problem on a given architecture.

CASCH includes various algorithms (see Figure 1) which are suitable to various environments. Currently, CASCH includes three classes of algorithms [2]: the UNC (unbounded number of clusters), the BNP (bounded number of processors), and the APN (arbitrary processor network) scheduling algorithms. The UNC scheduling algorithms, which are mostly based on clustering techniques, are designed for scheduling with unlimited number of processors. The BNP scheduling algorithms, which are based on the list

Figure 1: The system organization of CASCH.

scheduling technique [1], are suitable for scheduling when only a limited number of processors are available. The APN scheduling algorithms, which take into consideration link contention and the topology of target processor network, are useful for scheduling a distributed system.

**Communication Insertion and Code Generation:** Synchronization among the tasks running on multiple processors is carried out by communication primitives. The basic communication primitives for exchanging messages between processors are send and receive. They must be used properly to ensure a correct sequence of computation. These primitives are inserted automatically, reducing programmer's burden and eliminating insertion errors. The procedure for inserting communication primitive is as follows. After scheduling and mapping, each node in a macro dataflow graph is allocated to a processor. If an edge leaves from a node to another node which belongs to a different processor, the send primitive is inserted after the node. Similarly, if an edge comes from another node in a different processor, the *receive* primitive is inserted before the node. However, if a message has already been sent to a particular processor, the same message does not need to be sent to the same processor again. If a message is to be sent to many processors, broadcasting or multicasting can be applied instead of separate message. After the communication primitives are properly inserted, parallel code is generated by including appropriate library procedures from a standard package such as the NX of the Intel Paragon.

#### **3** Performance Results

CASCH runs on a SUN workstation that is linked through a network to an Intel Paragon. We have parallelized several applications on CASCH by using the scheduling algorithms described above (see Figure 1). In this paper we discuss the performance of two applications: Gaussian elimination and Laplace equation solver. The objective of including these results is to demonstrate the viability and usefulness of CASCH as well as to make a comparison among various scheduling algorithms. For reference, we have also included the results obtained with manually generated code. A manual code is generated by first partitioning the data among processors in a fashion that reduces the dependencies among these partitions. Based on this partitioning, an SPMD-based code is generated for each processors.

The performance measures include the program execution time (the maximum finish time out of all processors) measured on the Intel Paragon, the number of processors used by the schedule (and hence by the application program) generated by the scheduling algorithm, and the running time of the scheduling algorithm.

The first set of results (see Figure 2) are for the Gaussian climination application with four different sizes of input matrix dimensions: 4, 8, 16, and 32. Figure 2(a) shows the execution times for various data sizes using different algorithms. We observe that the execution times vary considerably with different algorithms. Among the UNC algorithm, the DCP algorithm yields the best performance due to its superior scheduling method. Among the BNP algorithms, MCP and DLS are in general better, primarily because of their better task priority assignment methods. Among the APN algorithms, BSA and MH perform better,

| Matrix Dimension                                                          |                                              |                                                                     |                                              |                                              |  | Matrix Dimension                          |                            |                            |                                  |                                        |  |

|---------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|--|-------------------------------------------|----------------------------|----------------------------|----------------------------------|----------------------------------------|--|

| Algorithm                                                                 | 4                                            | 8                                                                   | 16                                           | 32                                           |  | Algorithm                                 | 4                          | 8                          | 16                               | 32                                     |  |

| Manual                                                                    | 0.14                                         | 0.42                                                                | 2.42                                         | 4.52                                         |  | Manual                                    | 4                          | 8                          | 16 '                             | 32                                     |  |

| DCP<br>DSC<br>EZ<br>LC<br>MD                                              | 0.10<br>0.11<br>0.12<br>0.10<br>0.11         | $\begin{array}{c} 0.11 \\ 0.14 \\ 0.15 \\ 0.13 \\ 0.13 \end{array}$ | 0.28<br>N.A.<br>0.32<br>0.32<br>0.30         | 1.21<br>N.A.<br>1.38<br>1.42<br>1.29         |  | DCP<br>DSC<br>EZ<br>LC<br>MD              | 3<br>5<br>1<br>8<br>2      | 7<br>22<br>2<br>16<br>3    | 10<br>95<br>15<br>32<br>4        | 22<br>128<br>33<br>64<br>7             |  |

| ETF<br>HLFET<br>ISH<br>LAST<br>MCP<br>DLS                                 | 0.11<br>0.11<br>0.12<br>0.11<br>0.11<br>0.11 | 0.13<br>0.14<br>0.14<br>0.16<br>0.16<br>0.14                        | 0.31<br>0.35<br>0.34<br>0.33<br>0.30<br>0.29 | 1.34<br>2.47<br>1.29<br>1.50<br>1.28<br>1.30 |  | ETF<br>HLFET<br>ISH<br>LAST<br>MCP<br>DLS | 3<br>3<br>2<br>1<br>3<br>3 | 7<br>7<br>9<br>5<br>7<br>7 | 16<br>16<br>21<br>13<br>16<br>16 | 32<br>32<br>56<br>29<br>32<br>32<br>32 |  |

| BSA<br>BU<br>DLS<br>MH                                                    | 0.11<br>0.11<br>0.11<br>0.12                 | 0.13<br>0.34<br>0.23<br>0.26                                        | 0.32<br>0.35<br>0.34<br>0.33                 | 1.42<br>1.52<br>1.39<br>1.28                 |  | BSA<br>BU<br>DLS<br>MH                    | 3<br>8<br>3<br>1           | 6<br>20<br>7<br>2          | 12<br>38<br>12<br>6              | 32<br>48<br>16<br>17                   |  |

| (a) Execution Times (sec.) on the Paragon. (b) Number of processors used. |                                              |                                                                     |                                              |                                              |  |                                           |                            | s used.                    |                                  |                                        |  |

| Matrix Dimension<br>(No. of Tasks)        |                                                      |                                              |                                              |                                              |  |  |  |  |

|-------------------------------------------|------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|--|--|--|--|

| Algorithm                                 | 4 (20)                                               | 8 (54)                                       | 16 (170                                      | 32 (594)                                     |  |  |  |  |

| DCP<br>DSC<br>EZ<br>LC<br>MD              | 6.22<br>0.04<br>6.19<br>0.05<br>6.21                 | 6.48<br>0.05<br>6.50<br>0.06<br>6.84         | 13.29<br>0.09<br>*14.81<br>0.08<br>38.91     | 281.54<br>0.23<br>330.15<br>0.27<br>2671.4   |  |  |  |  |

| ETF<br>HLFET<br>ISH<br>LAST<br>MCP<br>DLS | 0.05<br>0.06<br>0.05<br>0.05<br>0.05<br>0.05<br>0.04 | 0.07<br>0.07<br>0.07<br>0.08<br>0.07<br>0.08 | 0.21<br>0.15<br>0.08<br>0.24<br>0.09<br>0.28 | 2.26<br>0.69<br>0.32<br>2.23<br>0.40<br>2.84 |  |  |  |  |

| BSA<br>BU<br>DLS<br>MH                    | 0.74<br>0.36<br>1.74<br>0.75                         | 1.96<br>0.37<br>15.33<br>1.38                | 0.43<br>301.66                               | 224.05<br>0.97<br>7459.3<br>364.75           |  |  |  |  |

(c) Scheduling times (sec.) on a SPARC Station 2.

Figure 2: Execution times, number of processors used and scheduling times for the Gaussian elimination application.

due to their proper allocations of tasks and messages. All algorithms perform better than manually generated code: Compared to the manual scheduling, the level of performance improvement is up to 400%. The number of processors used by these algorithms is shown in Figure 2(b). The BU algorithm has a tendency of using a large number of processors. The times taken by various scheduling algorithms for generating the schedules for the Gaussian elimination example are included in Figure 2(c). We notice that these scheduling times vary drastically. The MD and DLS algorithms take considerably longer time to generate solutions while DSC and MCP are much faster.

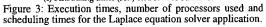

Our second application is a Gauss-Seidel based algorithm to solve Laplace equations. The 4 matrix sizes used are 4, 8, 16, and 32. The application execution times using various algorithms and data size are shown in Figure 3(a). Again, using the best algorithms, such as DCP, more than 400% improvement over manually generated code is obtained. The UNC algorithms in general yield better schedules (mainly because they tend to use large numbers of processors). The numbers of processors used by these algorithms are shown in Figure 3(b). Again, the number of processors used by the DSC algorithm is quite large as compared to the other algorithms. The running times of the scheduling algorithms are shown in Figure 3(c) which are consistent with our earlier observations.

A number of conclusions can be made from the above results. First, in general UNC algorithms generate shorter schedules but uses more processors than BNP and APN

| Matrix Dimension                                                          |                                                      |                                              |                                              |                                              |                                              |                                              | Matrix Dimension                         |                            |                            |                            |                             |

|---------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|------------------------------------------|----------------------------|----------------------------|----------------------------|-----------------------------|

| Algorithm                                                                 | 4                                                    | 8                                            | 16                                           | 32                                           | _                                            | Alg                                          | orithm                                   | 4                          | 8                          | 16                         | 32                          |

| Manual                                                                    | 0.72                                                 | 2.89                                         | 24.12                                        | 2 72                                         | .32                                          | Ma                                           | nual                                     | 2                          | 4                          | 8                          | 16                          |

| DCP<br>DSC<br>EZ<br>LC<br>MD                                              | 0.72<br>0.72<br>0.72<br>0.54<br>0.72                 | 1.06<br>1.34<br>1.44<br>1.25<br>1.25         | 6.08<br>6.30<br>6.95<br>6.95<br>6.52         | 16<br>18<br>18                               | .02<br>.42<br>.28<br>.81<br>.08              | DC<br>DS<br>EZ<br>LC<br>MI                   | С                                        | 1<br>1<br>1<br>2<br>1      | 4<br>7<br>8<br>4<br>4      | 4<br>4<br>2<br>4<br>3      | 8<br>14<br>39<br>8<br>6     |

| ETF<br>HLFET<br>ISH<br>LAST<br>MCP<br>DLS                                 | 0.72<br>0.72<br>0.72<br>0.72<br>0.72<br>0.72<br>0.72 | 1.25<br>1.34<br>1.34<br>1.54<br>1.54<br>1.34 | 6.73<br>7.60<br>7.39<br>7.17<br>6.52<br>6.30 | 32<br>17<br>19<br>16                         | .75<br>.71<br>.08<br>.87<br>.95<br>.22       | ET<br>HL<br>ISH<br>LA<br>MC<br>DL            | FET<br>I<br>ST<br>CP                     | 1<br>1<br>1<br>1<br>1<br>1 | 4<br>4<br>5<br>3<br>4<br>4 | 4<br>4<br>4<br>2<br>4<br>4 | 6<br>7<br>14<br>5<br>7<br>6 |

| BSA<br>BU<br>DLS<br>MH                                                    | 0.72<br>0.59<br>0.72<br>0.72                         | 1.25<br>3.26<br>1.92<br>1.92                 | 6.95<br>7.60<br>8.69<br>8.69                 | 20<br>23                                     | .81<br>.13<br>.25<br>.25                     | BS.<br>BU<br>DL<br>MI                        | S                                        | 1<br>2<br>1<br>1           | 5<br>5<br>1<br>1           | 4<br>5<br>1<br>1           | 7<br>5<br>1<br>1            |

| (a) Execution Times (sec.) on the Paragon. (b) Number of processors used. |                                                      |                                              |                                              |                                              |                                              |                                              |                                          |                            |                            |                            |                             |

| Matrix Dimension                                                          |                                                      |                                              |                                              |                                              |                                              |                                              |                                          |                            |                            |                            |                             |

| (No. of Tasks)<br>Algorithm 4 (18) 8 (66) 16 (258)32 (1026)               |                                                      |                                              |                                              |                                              |                                              |                                              |                                          |                            |                            |                            |                             |

| DCP<br>DSC<br>EZ<br>LC<br>MD                                              |                                                      |                                              | 0<br>8<br>0                                  | .58<br>.07<br>.63<br>.06<br>.58              | 7.03<br>0.04<br>7.15<br>0.07<br>7.65         | 9.60<br>0.10<br>9.71<br>0.09<br>10.01        | 44.95<br>0.29<br>35.00<br>0.16<br>111.99 |                            |                            |                            |                             |

| ETF<br>HLFET<br>ISH<br>LAST<br>MCP<br>DLS                                 |                                                      |                                              | .05<br>.08<br>.04<br>.08<br>.03<br>.05       | 0.07<br>0.09<br>0.08<br>0.10<br>0.04<br>0.07 | 0.10<br>0.11<br>0.09<br>0.15<br>0.10<br>0.10 | 0.30<br>0.29<br>0.35<br>0.82<br>0.19<br>0.36 |                                          |                            |                            |                            |                             |

| BSA<br>BU<br>DLS<br>MH                                                    |                                                      |                                              | 0<br>1<br>1                                  | .07<br>.47<br>.66<br>.00                     | 2.81<br>0.37<br>7.81<br>2.41                 | 4.92<br>0.50<br>10.86<br>3.25                | 27.99<br>0.73<br>75.90<br>16.29          | tion                       | 2                          |                            |                             |

| (c) Scheduling times (sec.) on a SPARC Station 2.                         |                                                      |                                              |                                              |                                              |                                              |                                              |                                          |                            |                            |                            |                             |

algorithms. Thus, UNC algorithms are more suitable for MPPs. Second, BNP algorithms require less time for scheduling than UNC and APN algorithms and therefore are more suitable for scheduling under time constraint. Finally, APN algorithms tend to use less processors, due to its consideration of link contention, but generate slightly longer schedules for the Intel Paragon which has a fast network. Thus, APN algorithms are more suitable for distributed systems such as a network of workstations (NOW).

#### **4** Conclusions and Future Work

The main objectives of CASCH are automatic parallelization and scheduling of applications to parallel processors. CASCH achieves these objectives by providing a unified environment for various existing and conceptual machines. Users can optimize their code by choosing the best algorithm. We are currently working on extending the capabilities of CASCH by including the following:

- including support for distributed computing systems such as a collection of diverse machines working as a distributed heterogeneous supercomputer system;

- extending the current database of benchmark timings by including more detailed and lower level timings of various computation, communication and I/O operations of various existing machines;

- · including debugging facilities for error detection and global variable checking, etc.;

- expressing various kinds of parallelism, use a functional or logic programming language or object oriented language such as C++;

• designing a partitioning module for automatic or interactive partitioning of programs.

### References

- [1] T.L. Adam, K.M. Chandy, and J. Dickson, "A Comparison of List Scheduling for Parallel Processing Systems," Comm. of the ACM, vol. 17, pp. 685-690, Dec. 1974. I. Ahmad, Y.-K. Kwok, and M.-Y. Wu, "Analysis, Evaluation

- [2] and Comparison of Algorithms for Scheduling Task Graphs to Parallel Processors," Proc. of the 1996 Int'l Symposium on Parallel Architecture, Algorithms and Networks, Beijing,

- [3]

- Parallel Architecture, Algorithms and Networks, Beijing, China, Jun. 1996, pp. 207-213.

B. Appelbe and K. Smith, "A Parallel-Programming Toolkit," *IEEE Software*, pp. 29-38, Jul. 1989.

J. Baxter and J.H. Patel, "The LAST Algorithm: A Heuristic-Based Static Task Allocation Algorithm," Proc. *ICPP*, vol. II, pp. 21222, Aug. 1989. [4] pp. 217-222, Aug. 1989. Cray Research Inc., UNICOS Performance Utilities Reference

- [5] Manual, sr2040 6.0 edition, 1991.

- Digital Equipment Corp., PARASPHERE User Guide.

- J.J. Dongarra and D.C. Sorensen, Schedule Users Guide, Tech. Rep. Version 1.1, Argonne National Lab., Jun. 1987. H. El-Rewini and T.G. Lewis, "Scheduling Parallel Programs

- [8] onto Arbitrary Target Machines," J. of Parallel and Dist. Computing, vol. 9, no. 2, pp. 138-153, Jun. 1990. B.C. Gorda and E.D. Brooks III., "Gang Scheduling a Parallel

- [9] machine," Technical Report UCRL--JC--107020, Lawrence Livermore National Laboratory.

- [10] High Performance Fortran Forum, High performance fortran language specification, Technical Report Version 1.0, Rice University, May 1993.

- [12] J.J.Hwang, Y.C. Chow, F.D. Anger and C.Y. Lee, "Scheduling Precedence Graphs in Systems with Interprocessor Communication Times," SIAM Journal of Computing, vol. 18,

- no. 2, pp. 244-257, Apr. 1989. [13] K. Kennedy, K.S. McKinley, and C. Tseng, "Interactive Parallel Programming Using the Parascope Editor," IEEE Trans. Parallel and Dist. Systems, 2(3):329--341, 1991. [14] S.J. Kim and J.C. Browne, "A General Approach to Mapping of

- Parallel Computation upon Multiprocessor Architectures,' Proc. ICPP, vol. II, pp. 1-8, Aug. 1988.

- [15] Y.-K. Kwok and I. Ahmad, "Dynamic Critical-Path Scheduling: An Effective Technique for Allocating Task Graphs to Multiprocessors," *IEEE Trans. on Parallel and* Distributed Systems, vol. 7, no. 5, May 1996, pp. 506-521

- [16] —, "Bubble Scheduling: A Quasi Dynamic Algorithm for Static Allocation of Tasks to Parallel Architectures," Proceedings of the 7th IEEE Symposium on Parallel and Distributed Processing, Oct. 1995, pp. 36-43.

- Instributed Processing, Oct. 1995, pp. 30-43.

T.G. Lewis and H. El-Rewini, "Parallax: A Tool for Parallel Program Scheduling," *IEEE Parallel & Distributed Technology*, vol.1, no. 3, pp. 62-72, May 1993.

N. Mehdiratta and K. Ghose, "A Bottom-Up Approach to Task Scheduling on Distributed Memory Multiprocessor," Proc. *ICD*, vol.1 are 161, 154, Aug. 1004.

- *ICPP*, vol. II, pp. 151-154, Aug. 1994. [19] D. Pease, A. Ghafoor, I. Ahmad, K. Foudil-Bey, D. Andrews, T. Karpinski, M. Mikki and M. Zerrouki, "PAWS: A performance Assessment Tool for Parallel Computing Systems," *IEEE Computer*, vol. 24, no. 1, pp. 18-29, Jan. 1991.

- [20] V. Sarkar, Partitioning and Scheduling Parallel, Programs for Multiprocessors, MIT Press, Cambridge, MA, 1989.

[21] G.C. Sih and E.A. Lee, "A Compile-Time Scheduling Heuristic

- for Interconnection-Constrained Heterogeneous Processor Architectures," IEEE Trans. on Parallel and Distributed Systems, vol. 4, no. 2, pp. 75-87, Feb. 1993.

- Systems, vol. 4, no. 2, pp. 13-67, Feb. 1755.

[22] M. Wolfe, "The Tiny Loop Restructuring Research Tool," Proc. *ICPP*, vol. II, pp. 46-53, Aug. 1991.

[23] M.-Y. Wu and D.D. Gajski, "Hypertool: A Programming Aid for Message-Passing Systems," *IEEE Trans. Parallel and Distributed Systems*, 1(3):330-343, Jul. 1990.

[24] T. Vacanard A. Goracoulia "PVPROS: Static Task Scheduling."

- [24] T. Yang and A. Gerasoulis, "PYRROS: Static Task Scheduling and Code Generation for Message-Passing Multiprocessors, The 6th ACM Int'l Conf. on Supercomputing, Jul. 1992.